“摩爾定律”曾主宰著半導體芯片一次次創造技術發展的奇跡,但近年來關于“摩爾定律”放緩甚至終結的聲音愈演愈烈,“后摩爾時代”成為行業一大熱詞。

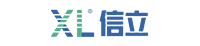

新工藝制程發展讓芯片體積性能不斷迭代,同時帶來了高昂的科研成本:據IBS統計,一個28nm芯片的設計成本在4000萬美元,16nm芯片設計成本約1億美元,而5nm芯片的設計成本更高達5.4億美元。工藝微縮的前景幾乎打破摩爾定律 “投資發展制程——芯片生產成本降低——制程再投資”的邏輯。

來源:International Business Strategies (IBS)

在延伸“摩爾定律”的道路上,Chiplet(芯粒)生逢其時。

3月2日,英特爾聯合10家芯片巨頭成立Chiplet標準聯盟,正式推出Chiplet(芯粒)的通用標準“UCle”(Universal Chiplet Interconnect Express通用芯粒互連),用來打通各家芯片鏈接協議,構建一個開放可互操作的Chiplet生態系統。

正當業內詫異Chiplet聯盟成員沒有蘋果、遺憾沒有中國大陸芯片廠商問津時,3月14日,來自芯東西的一篇報道,透露出國內Chiplet標準即將面世的消息,國標Chiplet草案已制訂完畢并有望在2022年第一季度公示,今年年底將進行《小芯片接口總線技術要求》初版標準發布,或將成為國產芯片打破制程封鎖,實現彎道超車的重要引擎。

小芯片“續寫”摩爾定律?

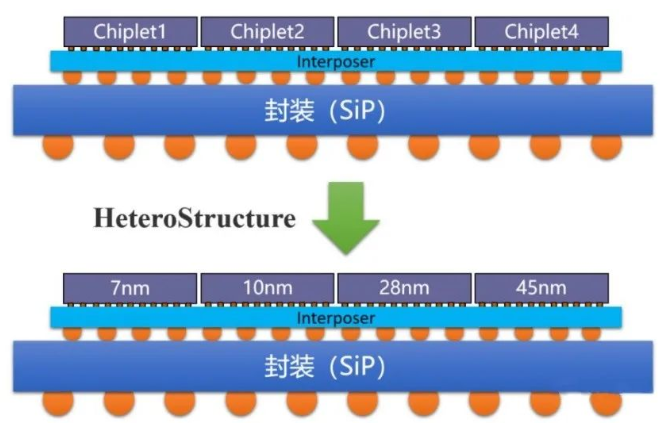

作為先進封裝技術的代表,Chiplet走向了和傳統SoC完全不同的道路。它將復雜芯片拆解成一組具有單獨功能的小芯片單元die(裸片),通過die-to-die將模塊芯片和底層基礎芯片封裝組合在一起,類似于搭建樂高積木,形成一個系統芯片。

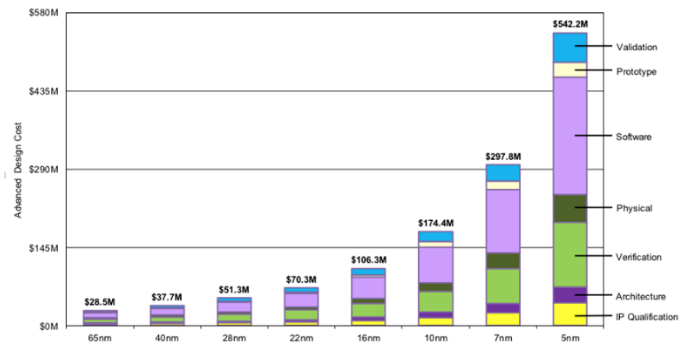

Chiplet的概念早在10余年前就被提出,Marvell創始人周秀文博士在ISSCC2015大會上提出了提出Mochi架構的概念,他認為Mochi可成為諸多應用的基礎架構。幾年后,這個概念開花結果,在經濟優勢和市場驅動下,AMD、臺積電、英特爾、英偉達等芯片巨頭廠商嗅到了這個領域的市場機遇,形成了現在的Chiplet。

使用Chiplet 的好處很多,以SoC為代表的集成芯片正面臨經濟邊界和物理邊界兩大難題:一是先進制程工藝成本高昂,二是模擬電路、I/O 等愈來愈難以隨著制程技術縮小。

而Chiplet在理論上完美補足了這兩個“缺陷”,用成熟的工藝把大芯片分成小芯片,能通過量產有效改善良率,同時降低制造成本。根據研究人員分析,這項技術可以將大型7nm設計的成本降低高達25%;在5nm及以下的情況下節省成本更大。

其次,Chiplet可以降低微縮設計的復雜程度與設計成本,以電路分割的小芯片各自強化相應功能、制程技術、尺寸,最后整合在一起,以克服制程微縮的挑戰。

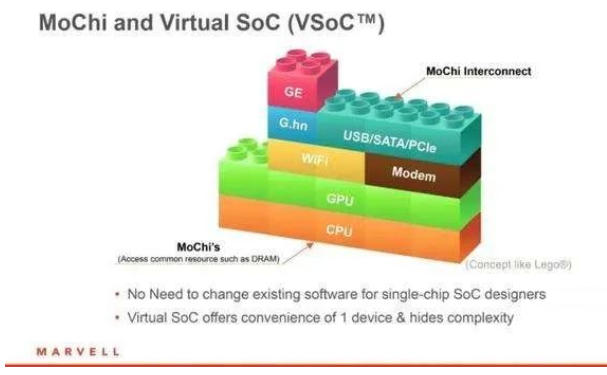

3月初Apple春季發布會上曝光的“宇宙級處理器”M1 Ultra 就是用兩個M1芯片采用UltraFusion的架構封裝技術完成的,搭載了1140億個晶體管。根據蘋果和臺積電公布的專利論文來看,業內人士猜測,UltraFusion應是基于臺積電第五代CoWoS Chiplet技術的互連架構。M1 ultra芯片充分顯示了Chiplet在封裝互連技術、半導體制造和電路設計上的巨大想象空間。

圖源:蘋果

蘋果M1的工藝思路,與我國即將推出的Chiplet標準技術不謀而合。

彎道超車:中國特色的Chiplet標準

對我國半導體產業而言,Chiplet被認為是與國外差距較小的先進封裝技術,被看作是后摩爾時代中國集成電路企業突破的希望,越來越多的企業與工廠加大對Chiplet的研發:華為是國內最早嘗試Chiplet的一批公司,海思半導體在早期就與臺積電合作過Chiplet技術,國產芯片廠商芯動科技在一款高性能服務器級顯卡GPU上使用了INNOLINK Chiplet技術……

小芯片有著卓越的經濟優勢,但作為新生技術也面臨不少挑戰。困于不同架構、不同制造商生產的die之間的互連接口和協議的不同,Chiplet的研發者在設計之初就得考慮工藝制程、封裝技術、系統集成、擴展傳輸等諸多復雜因素,這使得Chiplet的設計過程異常艱難。AMD的高級研究員Bryan Black概述了Chiplet芯片設計的九個考慮和挑戰:

如何在一個系統中劃分die

設計重用

管理參數變化

功率輸出

連接速度

劃分開銷

全局時鐘

die的安全

熱管理

樂高玩具之所以全球風行,基礎在于其積木模件的標準化,而Chiplet除了工藝設計之外的另一個難題,是die-to-die互聯的標準化。

在UCle出現之前,眾多芯片廠商都在“自說自話式”推廣自家互聯標準:如英偉達推出用于GPU的高速互聯NV Link方案;Intel免費向外界授權的AIB接口總線協議;臺積電也有TSMC和ARM合作搞了LIPINCON協議;AMD主張的Infinity Fabrie總線互聯技術,以及用于存儲芯片堆疊互聯的HBM接口等等。

UCle的推行,讓本在市場上互相傾軋的幾大巨頭開始攜手抱團,可見Chiplet的商業價值與無限潛力。開始推廣Chiplet標準化的時代就這樣悄然來臨。

面對UCle的出現,芯謀研究分析師認為,“我們要繼續走好自己的路,在加速國產化替代的同時,做好應對一切沖擊的準備,UCIe提供了一種可參考的產業平臺機制,我們亦可以通過組建內部產業聯盟的方式來優化產業分工,進一步加快國內產業發展,提高國內半導體產業對于沖擊的耐受力。”

在2021年1月,國內半導體巨頭華為海思牽頭,與中芯國際、紫光展銳、長江存儲、龍芯等國產半導體相關企業,組建了中國國產芯片聯盟。2021年5月,中國計算機互連技術聯盟(以下簡稱CCITA)在中電標協立項了Chiplet標準——《小芯片接口總線技術要求》,由國家部委和多個芯片廠商合作展開標準制定工作。

據“芯東西”報道,《小芯片接口總線技術要求》草案現已制訂完畢,即將進入征求意見階段,預計第一季度掛網公示和意見征集,第二季度完成技術驗證計劃制訂,2022年底前完成技術驗證和確定標準文本,并發布首個可用的Chiplet協議版本。

CCITA秘書長、中科院計算所研究員郝沁汾認為,“集成電路互連技術現階段對我們國家的價值,主要是解決我們完全無法使用先進制程的問題,如采用28nm的芯片,通過chiplet的方式,使其性能和功能接近16甚至7nm工藝的芯片性能。”

解決互聯標準只是第一步,在技術層面,Chiplet 還面臨著來自先進封裝、測試、軟件配合等多個方面的挑戰,郝沁汾坦言,“但是做到像PCIe、CXL這樣的普及程度,還需要更長時間,也需要國內企業的支持。”

學界人士也指出,在目前芯片工藝被國際形勢“卡脖子”的情況下,通過研究Chiplet先進封裝,在一定程度上“繞開”被卡的技術難點,甚至實現所謂的“彎道超車”、“換道超車”是很多人自然而然的想法,但集成電路產業的積累不是短時間可以完成的,Chiplet不是救市良方也不是靈丹妙藥,它不過是一種技術發展的思路而已,國內廠商要走“自研”路線,仍需打磨很長時間。

而對整個IOT行業來說,面對最大的痛點——碎片化,Chiplet為我們提供了一種組裝化的思路,去面對技術碎片化、應用碎片化,當我們將這個思路擴展,用不同的物聯網技術去組合搭載解決碎片化的場景,就讓1+1>2成為可能。

返回列表